# Nonvolatile Memory Cells Based on MoS<sub>2</sub>/Graphene Heterostructures

# Simone Bertolazzi, Daria Krasnozhon, and Andras Kis\*

Electrical Engineering Institute, École Polytechnique Fédérale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland

## ABSTRACT

Memory cells are an important building block of digital electronics. We combine here the unique electronic properties of semiconducting monolayer MoS<sub>2</sub> with the high conductivity of graphene to build a 2D heterostructure capable of information storage. MoS<sub>2</sub> acts as a channel in an intimate contact with graphene electrodes in a field-effect transistor geometry. Our prototypical all-2D transistor is further integrated with a multilayer graphene charge trapping layer into a device that can be operated as a nonvolatile memory cell. Because of its band gap and 2D nature, monolayer MoS<sub>2</sub> is highly sensitive to the presence of charges in the charge trapping layer, resulting in a factor of 10<sup>4</sup> difference between memory program and erase states. The two-dimensional nature of both the contact and the channel can be harnessed for the fabrication of flexible nanoelectronic devices with large-scale integration.

**KEYWORDS:** two-dimensional materials · dichalcogenides · MoS<sub>2</sub> · graphene · nanoelectronics · memory · heterostructures

wo-dimensional materials, such as graphene and single layers of boron nitride (BN) or molybdenum disulfide (MoS<sub>2</sub>), are the thinnest known materials with electronic properties that can be advantageous for a wide range of applications in nanotechnology.<sup>1–6</sup> Being only one layer thick, they represent the ultimate limit of scaling in the vertical direction and could offer reduced power dissipation because of smaller short channel effects.<sup>7</sup> They can also be regarded as a complete material library containing all the components necessary for building electronic circuits in which insulating BN could act as the substrate and gate dielectric barrier,<sup>6</sup> graphene as an interconnect while MoS<sub>2</sub> or another 2D semiconductor could play the role of a semiconducting channel.<sup>4</sup> Because graphene is semimetallic, it could form the ideal contact to 2D semiconductors, capable of supporting large current densities,<sup>8</sup>

exceeding 10<sup>9</sup> A/cm<sup>2</sup> (ref 9). Furthermore, the lack of dangling bonds at the interface between graphene and 2D semiconductors would suppress the appearance of interface states and charge traps. As the graphene's work function can be electrostatically or chemically tuned,<sup>10</sup> it could also be adapted to a wide variety of 2D semiconductors with different work functions and band gaps. In this work, we demonstrate the integration of a 2D semiconductor in the form of monolayer MoS<sub>2</sub> with graphene electrodes. The basic device functions as a field-effect transistor, with ohmic contacts and performance comparable to similar devices with metal contacts.<sup>4</sup> Furthermore, this device can serve as a prototype for more advanced devices based on a 2D architecture. We demonstrate this by adding a charge trapping layer in the form of a multilayer graphene floating gate, resulting in a new heterostructure capable of operating as a nonvolatile memory cell.

\* Address correspondence to andras.kis@epfl.ch.

Received for review December 21, 2012 and accepted March 13, 2013.

Published online March 19, 2013 10.1021/nn3059136

© 2013 American Chemical Society

VOL.7 • NO.4 • 3246-3252 • 2013

The use of 2D materials could offer immediate practical advantages for the realization of memory devices based on the floating gate transistor structure.<sup>11</sup> In current flash memory technology, serious hurdles need to be overcome to advance device miniaturization, both in the lateral and vertical directions. Vertical scaling leads to reduction of the program/erase voltages but is limited by the requirement of charge retention on the floating gate, which sets the limit for a minimum tunneling oxide thickness ( $\sim$ 5 nm). On the other hand, lateral scaling, driven by the guest for higher data storage capability, is seriously limited by the capacitive coupling between the drain electrode and the floating gate, which results in a longer penetration of the drain field in the transistor channel<sup>12</sup> as the device is scaled. Furthermore, interference between neighboring cells leads to an undesirable spread in the threshold voltages of the devices.<sup>13</sup> The effect of capacitive interference can be significantly diminished through the reduction of the floating gate thickness,<sup>14</sup> while the reduction of electrode thickness can diminish the coupling between the electrodes and the floating gate. Because of this, it is extremely interesting to investigate the suitability of 2D materials for use in memory devices where they could replace traditional choices for semiconducting channels, interconnects, and charge trapping layers.

## **RESULTS AND DISCUSSION**

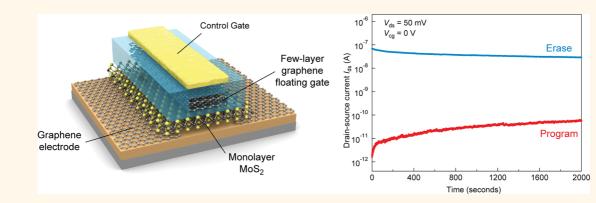

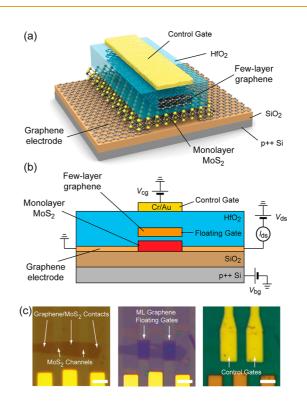

Figure 1 shows the structure of our memory device, composed of two transistors fabricated on the same monolayer MoS<sub>2</sub> flake placed over graphene stripes acting as source and drain electrodes. A piece of multilayer graphene (MLG), 4–5 layers thick, separated by a 6 nm thick tunneling oxide layer (HfO<sub>2</sub>) from the monolayer MoS<sub>2</sub> channel acts as the floating gate. We chose multilayer graphene as the floating gate because of its work function (4.6 eV) which is not sensitive to the number of layers and results in a deep potential well for charge trapping and improved charge retention. Furthermore, the low conductivity along the vertical c-axis suppresses detrimental ballistic currents across the floating gate,<sup>15</sup> while a higher density of states (>4.4  $\times$  10  $^{\bar{13}}\,\text{cm}^{-2}\,\text{eV}^{-1}$  ) with respect to its single-layer counterpart (8  $\times$  10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup>)<sup>16</sup> would allow more charge to be stored on it resulting in a larger memory window. The floating gate is further capped by a 30 nm thick blocking oxide layer at the top. The conductivity of the MoS<sub>2</sub> channel depends on the amount of charge stored in the floating gate (FG) and is modulated by the voltage  $V_{cq}$  applied to the control gate electrode (CG), which can also be used to vary the amount of charge stored on the floating gate.

The fabrication process includes three transfer steps.<sup>17</sup> Figure 1C shows the appearance of the device at several stages of the fabrication procedure. We start by growing graphene using chemical vapor deposition (CVD)<sup>18</sup> and transferring it onto a silicon substrate with

Figure 1. MoS<sub>2</sub>/graphene heterostructure memory layout. (a) Three-dimensional schematic view of the memory device based on single-layer MoS<sub>2</sub>. (b) Schematics of a heterostructure memory cell with a single-layer MoS<sub>2</sub> semiconducting channel, graphene contacts and multilayer graphene (MLG) floating gate. The MLG floating gate is separated from the channel by a thin tunneling oxide (ca. 1 nm  $AI_2O_3 + 6$  nm  $HfO_2$ ) and from the control gate by a thicker blocking oxide (1 nm  $AI_2O_3 + 30$  nm  $HfO_2$ ). (c) Optical micrographs of two graphene/MoS<sub>2</sub> heterostructure transistors fabricated on the same MoS<sub>2</sub> monolayer flake at various stages of fabrication. Left: single-layer MoS<sub>2</sub> transferred over an array of graphene stripes patterned on oxidized silicon chips and contacted with metal leads (Cr/Au: 10/50 nm); middle: the same device after deposition of the tunneling oxide and transfer/ patterning of MLG floating gates; right: final device after the deposition of the blocking oxide and definition of the control gate electrodes (Cr/Au: 10/50 nm). Scale bars: 3  $\mu$ m.

a 270 nm thick thermally grown silicon-dioxide (SiO<sub>2</sub>) laver. Graphene is patterned into stripes and contacted with metal leads. MoS<sub>2</sub> is then exfoliated on another SiO<sub>2</sub>/ Si substrate covered with a sacrificial polymer layer. Individual layers are detected using optical microscopy<sup>19</sup> and transferred<sup>20</sup> on top of the graphene stripes that form the source and drain electrodes in direct contact with monolayer MoS<sub>2</sub>. Fabrication continues with the deposition of the tunneling oxide layer on top of the MoS<sub>2</sub>/ graphene heterostructure, in the form of a 6 nm thick HfO<sub>2</sub> film grown using atomic layer deposition (ALD). We use a thermally oxidized AI seed layer<sup>21</sup> to facilitate the ALD deposition over graphene and MoS<sub>2</sub>. Multilayer graphene flakes 1.5 nm thick are transferred onto the tunneling oxide and positioned above the MoS<sub>2</sub> flakes. Finally, the floating gate is capped by a 30 nm thick HfO<sub>2</sub> layer followed by the deposition of the control gate.

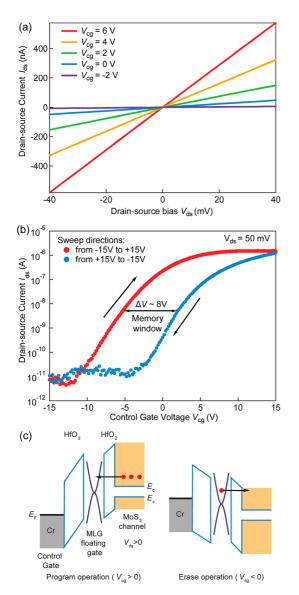

Figure 2a shows the small-bias current versus bias voltage  $(I_{ds} - V_{ds})$  characteristic of one of our floating

VOL.7 • NO.4 • 3246-3252 • 2013

IAI

www.acsnano.org

Figure 2. Device characteristics and charge trapping in the device. (a) Output characteristics (drain-source current Ids vs drain-source voltage  $V_{ds}$ ) of the floating gate transistor in the ON state, for different control gate biases V<sub>cg</sub>. The curve linearity at small  $V_{ds}$  indicates that graphene acts as a ohmic contact to monolayer MoS<sub>2</sub>. (b) Transfer characteristic (drain-source current  $I_{ds}$  vs control-gate voltage  $V_{ca}$ ) of the floating gate transistor, acquired along two different control-gate voltage sweep directions. The large hysteresis of  $\sim$ 8 V is related to accumulation of charge in the MLG floating gate. The voltage sweep rate was 1.4 V/s. (c) Simplified band diagram of the memory device in program and erase states. Application of a positive control gate voltage  $V_{cq}$  programs the device. Electrons tunnel from the MoS<sub>2</sub> channel through the 6 nm thick HfO<sub>2</sub> and accumulate on the multilayer graphene floating gate. Application of a negative control gate voltage  $V_{cq}$  depletes the floating gate and resets the device.

gate transistors acquired for different values of the control gate voltage  $V_{cg}$ . The symmetry of the curves with respect to the origin and their linear behavior indicates the formation of ohmic contacts between graphene and monolayer MoS<sub>2</sub>. This is due to a tunable and favorable graphene work function.<sup>10</sup> The relatively

large current, on the order of 500 nA for a 40 mV bias, corresponding to a total series resistance of 125 kOhm shows that efficient charge injection from graphene to MoS<sub>2</sub> is possible even though the distance between the two is close to the interlayer distance in graphite (3.4 Å). This is in agreement with density functional theory-based calculations of the electronic structure of graphene/MoS<sub>2</sub> hybrids showing that charge transfer between graphene and MoS<sub>2</sub> is possible in spite of a lack of interaction and the relatively large interlayer separation.<sup>22</sup>

As this device is in two-contact configuration, we can only estimate the upper limit for the contact resistance from the highest recorded channel current during the gate voltage sweep shown on Figure 2a. From  $I_{ds} = 1.5 \,\mu$ A, a bias voltage  $V_{ds}$  = 50 mV, and channel width of 3  $\mu$ m, we estimate the upper limit for the contact resistance of 50 k $\Omega \cdot \mu$ m. Future four-contact and transfer-length measurements will result in a more accurate measurement of contact resistance in this material combination. This value could be further reduced by chemical doping, local electrostatic control or the use of flat substrates. The use of graphene as a contact material for 2D semiconductors in place of thicker metallic films is expected to be advantageous as it allows fabricating devices and circuits<sup>23</sup> in a truly 2D architecture, using for example roll-to-roll printing and with reduced parasitic interference between neighboring devices and increased resistance to short-channel effects.<sup>7</sup> Work-function tunability<sup>10</sup> of graphene will allow it to be adapted to a wide variety of 2D materials. Furthermore, because it is chemically inert and mechanically flexible, graphene is the ideal noninvasive contact to other 2D materials.

The information storage capability of our device can be deduced from the transfer characteristics (drain current  $I_{ds}$  versus control-gate voltage  $V_{cq}$ ), shown in Figure 2b, acquired in two sweeping directions, from negative to positive voltages (blue) and in the opposite sweep direction (red). The large hysteresis, characterized by a maximum voltage shift  $\Delta V$  of approximately 8 V, is related to the charging/discharging of the floating gate in response to the control gate voltage. As the control gate voltage is swept toward high positive values (red curve), Fowler-Nordheim electron tunneling occurs from the channel into the floating gate through the HfO<sub>2</sub> oxide barrier, Figure 2c.<sup>24</sup> At this stage, electrons are accumulated in the floating gate and the device is in the program state. Accumulation of electrons in the floating gate results in a positive shift of the threshold voltage. This is observable from the blue curve, where the control gate voltage is swept in the opposite direction. As the control gate voltage  $V_{cq}$ reaches negative values, electrons are transferred back from the floating gate to the channel. For sufficiently high fields the floating gate is fully discharged, resulting in the erase state. For the purpose of reading the

JAI

memory state, zero voltage should be applied to the control gate ( $V_{cg} = 0$ ). This would result in high drain current in the erase state and low drain current current in the program state.

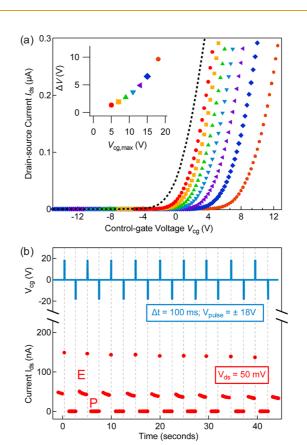

Other hysteresis mechanisms<sup>25</sup> could be present in the device, but they can be ruled out as potential sources of such a high memory effect. Trapping states related to charge impurities present at the semiconductor/dielectric interface cannot generate a permanent threshold voltage shift. As shown in Figure 3a, we can generate permanent current/threshold voltage states characterized by varying memory windows  $\Delta V$ by modulating the amount of charge stored in the floating gate. To calculate the threshold voltage shift, we define a reference erase state by assuming that the floating gate is not likely to accumulate positive charge (see Supporting Information). The floating gate can be depleted of all residual charge by sweeping the control gate voltage from 0 V to a low negative voltage, denoted as  $V_{cg,min}$  (<-5 V). This places the device in the erase state. Immediately after floating gate depletion, we sweep the control gate voltage in the negativeto-positive direction, starting from  $V_{cg,min} = -18$  V, resulting in the black dashed line in Figure 3a, characterized by a threshold voltage  $V_{\rm th}$  pprox 0 V. Repeating this voltage sweep results in a set of curves with no observable dependence of the  $V_{\rm th}$  on the different values tested for  $V_{\rm cg,min}$ .<sup>17</sup> This indicates that the multilayer graphene floating gate is not likely to accumulate positive charge (holes) in response to a negative voltage applied to the control gate. Hence, a reference E state with  $V_{\rm th} \approx$  0 V could be defined, corresponding to approximately zero charge stored in the FG. We can now reach different program (P) states by performing successive  $V_{cq}$  sweeps, stopping at gradually increasing maximum values of V<sub>cg,max</sub>. Figure 3a shows a family of curves acquired in this way, corresponding to different program states characterized by their own memory windows. The threshold voltage shift  $\Delta V$  (memory window), measured from the reference E state, is strongly dependent on the maximum control gate voltage, as can be inferred from the inset graph in Figure 3a. A maximum control gate voltage of +18 V results in a memory window exceeding 8 V. Gate leakage during these measurements is less than 10 pA and is within the noise limits of our instrument (see Supporting Information).

We estimate the amount of charge stored on the floating gate from the expression  $n = (\Delta V \times C_{FG-CG})/q$ , based on the charge balance equation,<sup>26</sup> where *q* is the electron charge,  $\Delta V$  is the difference in the threshold voltage for read and erase states, while the  $C_{FG-CG}$  is the capacitance between the floating gate and the control gate, modeled as  $C_{FG-CG} = \varepsilon_0 \varepsilon_{bl}/d_{bl}$ , with  $\varepsilon_0$  the vacuum permittivity,  $\varepsilon_{bl}$  the relative dielectric constant of the HfO<sub>2</sub> blocking layer (~19), and  $d_{bl}$  its thickness (~30 nm). This results in a density of stored electrons

Figure 3. Memory states. (a) Dependence of the memory window on the control-gate voltage. Symbols: transfer characteristics (drain-source current Ids vs control-gate voltage  $V_{cg}$ ) of the floating gate transistor acquired from positive to negative control gate voltages  $V_{cg}$ , for different  $V_{cg,max}$  (plotted in the inset). The drain-source voltage  $V_{ds}$  is fixed to 50 mV. Dashed line: transfer curve of the device in the erase state, corresponding to no charge stored on the floating gate. The inset graph shows the dependence of the memory window, related to charging of the floating gate, on the maximum voltage applied to the control gate. (b) Switching between erase (E, high current, device ON) and program (P, low current, device OFF) states induced by the application of alternating  $V_{cg}$  pulses (±18 V for 100 ms) with a time interval of 2.3 s. The application of a positive  $V_{cq}$ pulse  $(E \rightarrow P)$  induces a drain-source current  $I_{ds}$  peak (130-150 nA) due to the increase of the charge density in the MoS<sub>2</sub> channel during the pulse.

on the order of  $\sim 2.8 \times 10^{13}$  cm<sup>-2</sup>. In agreement with Mishra *et al.*<sup>14</sup> and Hong *et al.*<sup>27</sup> we conclude that MLG, due to its higher density of states than in graphene, allows a larger memory window with strong potential for multilevel data storage.

We now test the dynamic behavior of our device, reported in Figure 3b. Switching between program and erase states is achieved through the application of voltage pulses to the control gate electrode, with the source grounded and the drain biased at 50 mV. The device is initially in the *E* state, corresponding to the ON current level. A positive voltage pulse (+18 V) with the duration of 100 ms leads to both accumulation of charge in the transistor channel, indicated by the ~150 nA current spike and to tunneling of electrons into the floating gate. When the control gate voltage is

reset to 0 V, the device remains in its program state, holding a stable OFF current. The application of a symmetric negative pulse (-18 V, 100 ms duration) 2.3 s later restores the initial erase state. We performed an endurance test measurement for our memory device, observing a well-defined and reproducible *P/E* switching for over 120 cycles. The slow decay of the ON current is presumably due to trapping mechanisms related to charge impurities present at the semiconductor/dielectric interface, as observed elsewhere.<sup>25</sup>

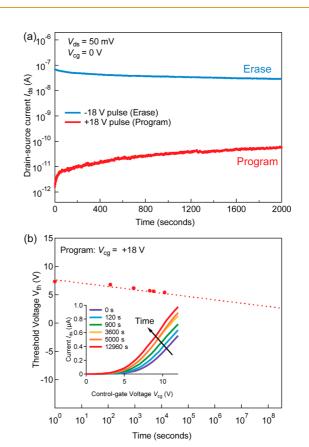

The stability of E and P states, crucial for nonvolatile information storage, was further investigated by monitoring their time-resolved behavior at a constant drain-source bias of 50 mV, reported in Figure 4. During the entire observation time, the corresponding erase state current was measured to be in the range  $10^{-8}$  –  $10^{-7}$  A, with an exponential decay saturating to about 20 nA. After this measurement, the memory was programmed to the program state through a voltage pulse ( $V_{cq} = +18$  V, duration 3 s), resulting in the OFF state of the drain current  $I_{ds}$ . Although slowly increasing with time, the  $I_{ds}$  current remained in the 10<sup>-12</sup>-10<sup>-10</sup> A range during at least 2000 s. Room for improvement can be identified in both lowering the density of charge impurities in and around the channel in order to stabilize the erase-state current and in improved engineering of the tunneling oxide layer to increase the retention performance.

For the program and erase states we measured a maximal program/erase (P/E) current ratio exceeding  $10^4$ . Such a remarkable P/E current ratio not only allows easy readout of the device state, but also allows multi-level storage, where more than one bit of information could be stored in the memory cell in the form of several distinct floating-gate charge levels.

As the final step of our device characterization procedure, we studied the memory charge retention characteristics (Figure 4b), which are related to both the nature of the tunneling barrier and to the work function of the MLG. The latter determines the depth of the potential well for the electrons stored in the floating gate. After programming the memory through a positive pulse ( $V_{cq} = +18$  V during 3 s), we measured the threshold voltage at different time intervals, determined using a linear fit of the transfer characteristics, as shown in the inset of Figure 4b. These curves were acquired in a narrow range of control voltage  $V_{ca}$ , from 0 to +12 V, in order to prevent undesired electron depletion/injection occurring at the floating gate. Successive voltage sweeps carried out immediately one after the other resulted in similar V<sub>th</sub> values, confirming the fact that the measurement itself was not perturbing the system. We observe a threshold voltage variation from 7.5 to 5 V during a time period of  $10^4$  seconds. Assuming that the reference erase state is characterized by  $V_{\rm th} \approx$  0 V, we estimate that, after 10 years, 30% of the initial charge would still be stored on the floating gate. This result proves that the charge leakage from

Figure 4. Device dynamics and charge retention. (a) Temporal evolution of drain-source currents ( $l_{ds}$ ) in the erase (ON) and program (OFF) states. The curves are acquired independently for the program ( $10^{-8}-10^{-7}$  A) and erase ( $10^{-12}-10^{-10}$  A) current states and plotted on a common time scale. The drain-source bias voltage is 50 mV and the duration of the control-gate voltage ( $V_{cg}$ ) pulse is 3 s. (b) Time-resolved behavior of the device threshold voltage after application of the programming voltage pulse (+18 V for 3 s). Threshold voltage was determined from linear fits to transfer curves (inset) in the linear regime. We estimate that after 10 years the device retains 30% of the charge stored on the floating gate.

the floating gate is slow on the time-scale of years and that the combination MoS<sub>2</sub>/MLG indeed has a potential for application in nonvolatile memory technology. The value extracted for charge retention appears encouraging, considering that this is the first prototype of its kind. Further improvement can be achieved by means of a thorough engineering of the blocking oxide layer, using for instance novel insulating 2D crystals, such as BN or 2D oxides.<sup>28</sup>

## CONCLUSION

We have demonstrated a new type of heterostructures based on 2D materials in which we use graphene as an ohmic contact to monolayer  $MoS_2$  in a field-effect transistor geometry, paving the way toward the realization of truly 2D device architectures. The final device includes a multilayer graphene floating gate and operates as a nonvolatile memory cell. This demonstrates that it is possible to design memory devices using 2D building blocks, including contacts, floating gate, and ARTICLE

VOL.7 • NO.4 • 3246-3252 • 2013

the semiconducting channel. Moreover, the excellent mechanical properties of 2D semiconductors such as  $MoS_2$  (ref 29) can be exploited for fabrication of transistor circuits and memory devices on flexible

substrates, with a naturally emerging range of related applications. Such devices could be produced massively and inexpensively using liquid-scale processing<sup>30</sup> or roll-to-roll printing<sup>31</sup> of CVD-grown material.<sup>32,33</sup>

### **METHODS**

Single layers of MoS<sub>2</sub> are exfoliated from commercially available crystals of molybdenite (SPI Supplies Brand Moly Disulfide) using the scotch-tape micromechanical cleavage technique method pioneered for the production of graphene.<sup>1</sup> AFM imaging was performed using the Asylum Research Cypher AFM. Electrical characterization of the memory device was performed in ambient conditions at room temperature using an Agilent E5270B parameter analyzer.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. Device fabrication was carried out in part in the EPFL Center for Micro/Nanotechnology (CMI). Thanks go to Zdenek Benes for technical support electron-beam lithography. We thank Branimir Radisavljevic and Jacopo Brivio for valuable discussions and Mahmut Tosun for technical help with CVD graphene growth. This work was financially supported by the Swiss National Science Foundation (Grant Nos. 138237 and 135046) and the Swiss Nanoscience Institute (NCCR Nanoscience).

Supporting Information Available: Detailed description of the device fabrication procedure and additional characterization of the device. This material is available free of charge via the Internet at http://pubs.acs.org.

## **REFERENCES AND NOTES**

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* 2004, 306, 666–669.

- Novoselov, K. S.; Jiang, D.; Schedin, F.; Booth, T. J.; Khotkevich, V. V.; Morozov, S. V.; Geim, A. K. Two-Dimensional Atomic Crystals. *Proc. Natl. Acad. Sci. U.S.A.* 2005, *102*, 10451– 10453.

- Dean, C. R.; Young, A. F.; Meric, I.; Lee, C.; Wang, L.; Sorgenfrei, S.; Watanabe, K.; T.; Kim, P.; Shepard, K. L.; et al. Boron Nitride Substrates for High-Quality Graphene Electronics. *Nat. Nanotechnol.* **2010**, *5*, 722–726.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* 2011, 6, 147–150.

- Britnell, L.; Gorbachev, R. V.; Jalil, R.; Belle, B. D.; Schedin, F.; Mishchenko, A.; Georgiou, T.; Katsnelson, M. I.; Eaves, L.; Morozov, S. V.; et al. Field-Effect Tunneling Transistor Based on Vertical Graphene Heterostructures. *Science* 2012, 335, 947–950.

- Britnell, L.; Gorbachev, R. V.; Jalil, R.; Belle, B. D.; Schedin, F.; Katsnelson, M. I.; Eaves, L.; Morozov, S. V.; Mayorov, A. S.; Peres, N. M. R.; et al. Electron Tunneling through Ultrathin Boron Nitride Crystalline Barriers. *Nano Lett.* **2012**, *12*, 1707–1710.

- 7. Yoon, Y.; Ganapathi, K.; Salahuddin, S. How Good Can Monolayer  $MoS_2$  Transistors Be? Nano Lett. **2011**, 11, 3768–3773.

- Moser, J.; Barreiro, A.; Bachtold, A. Current-Induced Cleaning of Graphene. *Appl. Phys. Lett.* 2007, *91*, 163513.

- Yu, J.; Liu, G.; Sumant, A. V.; Goyal, V.; Balandin, A. A. Graphene-on-Diamond Devices with Increased Current-Carrying Capacity: Carbon Sp2-on-Sp3 Technology. *Nano Lett.* **2012**, *12*, 1603–1608.

- 10. Yu, Y.-J.; Zhao, Y.; Ryu, S.; Brus, L. E.; Kim, K. S.; Kim, P. Tuning the Graphene Work Function by Electric Field Effect. *Nano Lett.* **2009**, *9*, 3430–3434.

- Kahng, K.; Sze, S. M. A Floating Gate and Its Application to Memory Devices. *IEEE Trans. Electron Devices* **1967**, *14*, 629–629.

- Chan, A. C. K.; Tsz-Yin, M.; Jin, H.; Kam-Hung, Y.; Wai-Kit, L.; Chan, M. SOI Flash Memory Scaling Limit and Design Consideration Based on 2-D Analytical Modeling. *IEEE Trans. Electron Devices* **2004**, *51*, 2054–2060.

- Jae-Duk, L.; Sung-Hoi, H.; Jung-Dal, C. Effects of Floating-Gate Interference on Nand Flash Memory Cell Operation. *IEEE Trans. Electron Devices* 2002, 23, 264–266.

- Misra, A.; Kalita, H.; Waikar, M.; Gour, A.; Bhaisare, M.; Khare, M.; Aslam, M.; Kottantharayil, A. In *Multilayer Graphene as Charge Storage Layer in Floating Gate Flash Memory*, Memory Workshop (IMW), 2012 4th IEEE International, Milan, Italy,20–23 May 2012; IEEE Conference Publications, **2012**; pp 1–4.

- Raghunathan, S.; Krishnamohan, T.; Parat, K.; Saraswat, K. In Investigation of Ballistic Current in Scaled Floating-Gate Nand Flash and a Solution, Electron Devices Meeting (IEDM), 2009 IEEE International, Baltimore, MD, Dec 7–9, 2009; IEEE Conference Publications, 2009; pp 1–4.

- Zhu, W.; Perebeinos, V.; Freitag, M.; Avouris, P. Carrier Scattering, Mobilities, and Electrostatic Potential in Monolayer, Bilayer, and Trilayer Graphene. *Phys. Rev. B* 2009, *80*, 235402.

- 17. Please refer to the Supporting Information for more information.

- Li, X.; Cai, W.; An, J.; Kim, S.; Nah, J.; Yang, D.; Piner, R.; Velamakanni, A.; Jung, I.; Tutuc, E.; et al. Large-Area Synthesis of High-Quality and Uniform Graphene Films on Copper Foils. *Science* **2009**, *324*, 1312–1314.

- Benameur, M. M.; Radisavljevic, B.; Héron, J. S.; Sahoo, S.; Berger, H.; Kis, A. Visibility of Dichalcogenide Nanolayers. Nanotechnology 2011, 22.

- Brivio, J.; Alexander, D. T. L.; Kis, A. Ripples and Layers in Ultrathin MoS<sub>2</sub> Membranes. *Nano Lett.* 2011, *11*, 5148–5153.

- Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. K. Realization of a High Mobility Dual-Gated Graphene Field-Effect Transistor with Al<sub>2</sub>O<sub>3</sub> Dielectric. *Appl. Phys. Lett.* **2009**, *94*, 062107–3.

- Ma, Y.; Dai, Y.; Guo, M.; Niu, C.; Huang, B. Graphene Adhesion on MoS<sub>2</sub> Monolayer: An Ab Initio Study. *Nanoscale* **2011**, *3*, 3883–3887.

- Radisavljevic, B.; Whitwick, M. B.; Kis, A. Integrated Circuits and Logic Operations Based on Single-Layer MoS<sub>2</sub>. ACS Nano 2011, 5, 9934–9938.

- Lenzlinger, M.; Snow, E. H. Fowler-Nordheim Tunneling into Thermally Grown SiO<sub>2</sub>. J. Appl. Phys. **1969**, 40, 278–283.

- Late, D. J.; Liu, B.; Matte, H. S. S. R.; Dravid, V. P.; Rao, C. N. R. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. ACS Nano 2012, 6, 5635–5641.

- Pavan, P.; Larcher, L.; Marmiroli, A. Floating Gate Devices: Operation and Compact Modeling; Kluwer Academic: Boston, 2004.

- Hong, A. J.; Song, E. B.; Yu, H. S.; Allen, M. J.; Kim, J.; Fowler, J. D.; Wassei, J. K.; Park, Y.; Wang, Y.; Zou, J.; et al. Graphene Flash Memory. ACS Nano 2011, 5, 7812–7817.

- Osada, M.; Sasaki, T. Two-Dimensional Dielectric Nanosheets: Novel Nanoelectronics from Nanocrystal Building Blocks. Adv. Mater. 2012, 24, 210–228.

- Bertolazzi, S.; Brivio, J.; Kis, A. Stretching and Breaking of Ultrathin MoS<sub>2</sub>. ACS Nano **2011**, *5*, 9703–9709.

- Coleman, J. N.; Lotya, M.; O'Neill, A.; Bergin, S. D.; King, P. J.; Khan, U.; Young, K.; Gaucher, A.; De, S.; Smith, R. J.; et al. Two-Dimensional Nanosheets Produced by Liquid Exfoliation of Layered Materials. *Science* **2011**, *331*, 568–571.

- 31. Bae, S.; Kim, H.; Lee, Y.; Xu, X.; Park, J.-S.; Zheng, Y.; Balakrishnan, J.; Lei, T.; Ri Kim, H.; Song, Y. I.; et al. Roll-to-Roll Production of 30-Inch Graphene Films for Transparent Electrodes. Nat. Nanotechnol. 2010, 5, 574-578.

- 32. Liu, K.-K.; Zhang, W.; Lee, Y.-H.; Lin, Y.-C.; Chang, M.-T.; Su, C.-Y.; Chang, C.-S.; Li, H.; Shi, Y.; Zhang, H.; et al. Growth of Large-Area and Highly Crystalline MoS<sub>2</sub> Thin Layers on Insulating Substrates. Nano Lett. 2012, 12, 1538-1544.

- 33. Zhan, Y.; Liu, Z.; Najmaei, S.; Ajayan, P. M.; Lou, J. Large-Area Vapor-Phase Growth and Characterization of Mos<sub>2</sub> Atomic Layers on a SiO<sub>2</sub> Substrate. Small 2012, 8, 966–971.

IAr